# Capitolato tecnico di gara

# **ASTRA – WP1.A – Crystal Eye EU-TEL**

# LOTTO 1

# 1. SOMMARIO

| 1.    | SOMMARIO                               | 1  |

|-------|----------------------------------------|----|

| 2.    | ELENCO ACRONIMI                        | 2  |

| 3.    | PREMESSA, OBIETTIVI ED OGGETTO DI GARA | 3  |

| 4.    | DESCRIZIONE DELLA FORNITURA            | 3  |

| 4.1.  | FORNITURA INERENTE IL P/L CRYSTAL EYE  | 4  |

| 4.1.1 | . DU O DETECTION UNIT                  | 4  |

| 4.1.2 | EU O ELECTRONICS UNIT                  | 5  |

| 4.1.3 | EH O EXTERNAL HARNESS                  | 7  |

| 4.2.  | FORNITURA INERENTE EU-TEL              | 7  |

| 5.    | DETTAGLI FORNITURA                     | 7  |

| 5.1.  | UP PIXEL                               | 7  |

| 5.2.  | DOWN PIXEL                             | 8  |

| 5.3.  | ACS                                    | 9  |

| 5.4.  | SIPM BOARD                             | 10 |

| 5.5.  | ELECTRONICS UNIT (EU)                  | 11 |

| 5.5.1 | . DAQ BOARD (A)                        | 11 |

| 5.5.2 | . TRIGGER BOARD (C)                    | 12 |

| 5.5.3 | . CONCENTRATORE (D)                    | 12 |

| 5.5.4 | . SISTEMA DI RIDONDANZA (E)            | 13 |

| 5.5.5 | . PAYLOAD POWER SUPPLY O (PS)          | 15 |

| 5.5.6 | BACKPLANE                              | 16 |

| 5.6.  | EU-TEL                                 | 16 |

| 6.    | PART LIST                              | 25 |

| 6.1.  | PROTOTIPO CRYSTAL EYE                  | 25 |

| 6.2.  | ALTRI MODELLI CRYSTAL EYE              | 26 |

| 6.3.  | EU-TEL                                 | 27 |

| 7.   | REQUISITI DI PROGETTO28                                                                           |  |

|------|---------------------------------------------------------------------------------------------------|--|

| 7.1. | REQUISITI DI PERFORMANCE28                                                                        |  |

| 7.2. | REQUISITI AMBIENTALI34                                                                            |  |

| 7.3. | BUDGET DI MASSA E POTENZA35                                                                       |  |

| 8.   | CONDIZIONI E TEMPI DELLA FORNITURA36                                                              |  |

| 8.1. | PRODOTTI CHE IL SOGGETTO AGGIUDICATARIO FORNISCE AL COMMITTENTE36                                 |  |

| 8.2. | RIUNIONI DI AVANZAMENTO (MILESTONE E SAL)37                                                       |  |

|      | ATTIVITÀ DI PROGETTAZIONE, REALIZZAZIONE E TEST DEL PROTOTIPO DI CRYSTAL EYE E<br>ZEM38           |  |

|      | ATTIVITÀ DI QUALIFICA SPAZIALE DELL'EM E PROGETTAZIONE, REALIZZAZIONE E TEST DELL'FM RYSTAL EYE43 |  |

# 2. ELENCO ACRONIMI

| ACS           | Anticoincidence System             |

|---------------|------------------------------------|

| CDR           | Critical Design Review             |

| CoG           | Center of Gravity                  |

| DU            | Detection Unit                     |

| DPCU          | Dew Power Control Unit             |

| EH            | External Harness                   |

| EM            | Engineering Model                  |

| ESR           | <b>Enhanced Specular Reflector</b> |

| EU            | Electronics Unit                   |

| <b>EU-TEL</b> | Electronic Unit Telescope          |

| FM            | Flight Model                       |

| GRB           | Gamma Ray Burst                    |

| GSSI          | Gran Sasso Science Institute       |

| HV            | High Voltage                       |

| HG            | High Gain                          |

| LE            | Low Energy                         |

| LG            | Low Gain                           |

| LV            | Low Voltage                        |

| ME            | Medium Energy                      |

| PCU           | Power Control Unit                 |

| PDR           | Preliminary Design Review          |

| P/L           | Payload                            |

| Red           | Redoundancy                        |

| SiPM          | Silicon Photomultiplier            |

| SM            | Structural Model                   |

| SoC           | System on Chip                     |

| SOC           | Status of Compliance               |

| TRB           | Test Review Board                  |

| WP            | Work Package                       |

|               |                                    |

## 3. PREMESSA, OBIETTIVI ED OGGETTO DI GARA

Nell'ambito delle attività dell'Ecositema dell'innovazione digitalizzazione e sostenibilità per l'economia diffusa nel Centro Italia (VITALITY, CUP: D13C21000430001), il GSSI è responsabile dello Spoke ASTRA (Advanced Space Technologies and Research Alliance).

Le attività oggetto della presente gara di appalto afferiscono al WP1 del progetto ASTRA, che prevede la realizzazione di diversi prototipi del detector Crystal Eye fino ad arrivare alla realizzazione di un payload (P/L) qualificato per lo spazio nonché la realizzazione dell'elettronica di readout e gestione del piano focale di un telescopio (EU-TEL) che integra le osservazioni di Crystal Eye.

Il P/L basa il suo principio di funzionamento sull'osservazione di raggi gamma di medio bassa energia (10 keV - 30 MeV).

Obiettivo del progetto Crystal Eye e EU-TEL è dunque lo sviluppo, test e validazione di nuove tecnologie per l'osservazione in orbita di raggi gamma associati a diversi fenomeni, sia di tipo astrofisico, fra cui prevalgono i gamma ray burst (GRB), che generati nell'atmosfera terrestre.

Il presente capitolato tecnico si riferisce alla fornitura di attività di progettazione ed ingegnerizzazione finalizzate a:

- Sviluppare e realizzare un prototipo per testare la fattibilità dell'assemblaggio meccanico e gli algoritmi di trigger per individuare una sorgente gamma

- sviluppare e realizzare l'EM (Engineering Model) del P/L Crystal Eye;

- sviluppare e realizzare l'elettronica di readout e controllo (EU-TEL)

Le attività riguarderanno la struttura meccanica, la sensoristica, l'elettronica e il supporto ai test necessari all'operatività e al raggiungimento degli obiettivi scientifici e tecnologici dei P/L.

## 4. DESCRIZIONE DELLA FORNITURA

La fornitura oggetto del presente capitolato tecnico riguarda attività di progettazione, ottimizzazione e ingegnerizzazione finalizzate allo sviluppo e alla realizzazione di un prototipo in scala ed EM del P/L Crystal Eye, nonché della scheda di controllo (EU-TEL).

Più dettagliatamente, il committente richiede:

- la progettazione, ottimizzazione, ingegnerizzazione, sviluppo e realizzazione della struttura meccanica, della struttura elettronica di prossimità, dell'elettronica di alimentazione, di processamento e di controllo, di tutta la componente software e firmware del P/L Crystal Eye, l'approvvigionamento della sensoristica necessaria, l'integrazione finale di prototipo in scala ed EM;

- la progettazione, ottimizzazione, ingegnerizzazione, sviluppo e realizzazione di EM ed FM dell'elettronica di controllo EU-TEL.

Le condizioni della fornitura con le diverse attività, milestone e deliverable oggetto del presente capitolato sono riassunti nel capitolo 8.

Nelle restanti descrizioni riportate nel capitolato tecnico, per scheda "concentratore" si intende la scheda elettronica di controllo.

All'atto della pubblicazione della presente procedura non è ancora definita la possibile piattaforma satellitare dove sarà alloggiato il P/L. A titolo di riferimento, nelle descrizioni riportate nel capitolato tecnico, sono stati utilizzati i dati della piattaforma NIMBUS, utilizzata dal GSSI in precedenti missioni e di proprietà della Fondazione Gran Sasso Tech.

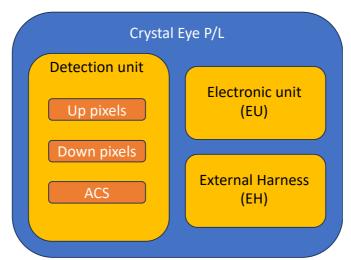

# 4.1. Fornitura inerente il P/L Crystal Eye

Il P/L Crystal Eye è costituito dai seguenti sottosistemi:

- 1. Detection Unit (DU);

- 2. Electronics Unit (EU);

- 3. External Harness (EH).

Le principali proprietà di ogni unità vengono descritte nelle seguenti sottosezioni del documento.

## 4.1.1. DU o Detection Unit

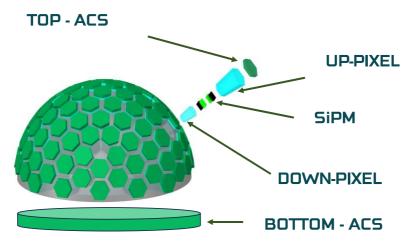

Crystal Eye è un detector di forma semisferica, modulare. Il suo diametro è compreso fra 30 e 40 cm. Il valore specifico sarà ottimizzato durante il progetto per massimizzare le capacità di rivelazione e restare nei limiti di peso e potenza imposti dalla piattaforma. Con riferimento alla Figura 1, la DU è formata dai seguenti sub-detector:

- **UP pixel**: shell intermedia costituita dall'insieme di cristalli scintillatori letti da Silicon PhotoMultiplier (SiPM), elettronica di front-end e dall'alloggiamento meccanico dedicato e a tenuta di luce;

- DOWN pixel: shell interna costituita dall'insieme di cristalli scintillatori letti da Silicon PhotoMultiplier (SiPM), elettronica di front-end e dall'alloggiamento meccanico dedicato e a tenuta di luce;

- AntiCoincidence System (ACS): insieme di una shell esterna e un disco alloggiato sotto il detector ciascuno costituito da scintillatore plastico letto da SiPM, elettronica di frontend e ciascuno inserito all'interno di un alloggiamento meccanico dedicato e a tenuta di luce;

Figura 1 Schema a blocchi del P/L.

La Figura 2 riporta schematicamente la configurazione dei componenti, distinti per colore, che costituiscono la DU.

Figura 2 Modello esploso del disegno di base del Crystal Eye- full detector

Dal punto di vista realizzativo la DU dovrà prevedere, inoltre, una interfaccia meccanica verso una potenziale piattaforma.

## 4.1.2. EU o Electronics Unit

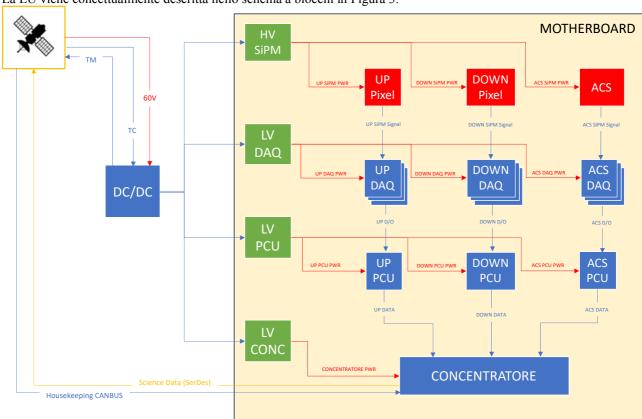

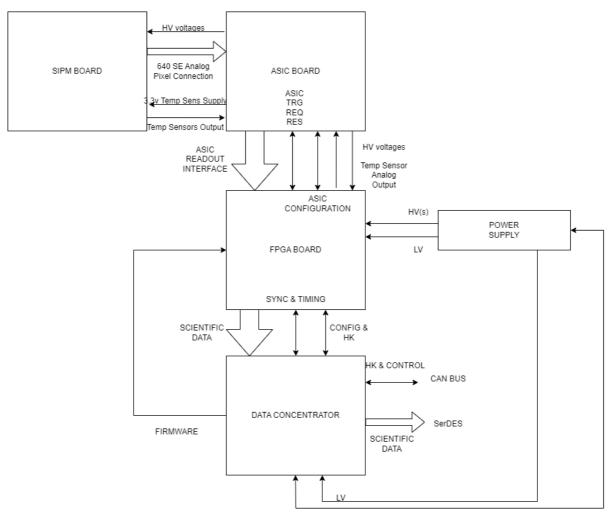

La EU viene concettualmente descritta nello schema a blocchi in Figura 3.

Figura 3 Schema a blocchi dell'unità elettronica del payload Crystal Eye.

Allo stadio di alimentazione DC/DC viene fornita una tensione di alimentazione non regolata compresa tra 60 V e 67.2V servita direttamente dell'Electric Power System della piattaforma ed ha il compito di generare blocchi di alimentazione primaria a servizio dei sottosistemi del P/L (tensione di

alimentazione SiPM (LV SiPM). La tensione primaria di alimentazione per le schede di lettura e processamento dati (LV DAQ e LV PCU), per le schede di concentrazione, raccolta dati e interfaccia satellite (LV PY e LV DPCU) sarà isolata.

A valle dello stadio di alimentazioni troviamo il gruppo di front end (rettangoli in rosso con riferimento alla Figura 3) nel quale vengono alloggiati i SiPM e gli altri fotosensori.

I segnali generati vengono poi acquisiti dalle schede (DAQ, blocchi in blu scuro) e preliminarmente processati (PCU, blocchi in blu scuro) prima dell'invio al Payload Controller per la costruzione dell'evento globale e al DPCU che agisce da interfaccia col sistema satellite.

La descrizione dettagliata e le richieste di funzionamento dei sottosistemi che compongono la DU sono riportate nelle sezioni 5 e 7.

Dal punto di vista costruttivo, la EU è costituita da un involucro in alluminio in grado di mantenere le schede in posizione durante il lancio, prevenendo rotture o disconnessioni causate dalle sollecitazioni della fase di lancio, di preservare le schede da danneggiamento (provvedendo cioè ad aumentare l'efficienza di schermo alla radiazione, pur mantenendo inalterati i requisiti sul budget di massa del sistema P/L), di garantire una adeguata dissipazione termica sulle superfici esterne del tray in cui è inserito il P/L e di poter accogliere tutte le connessioni richieste dal lato rivelatori (UP e DOWN Pixels e ACS).

La EU dovrà inoltre prevedere un sistema di aggancio meccanico al tray della piattaforma che sia progettato in modo tale da non violare nessuno dei requisiti meccanici imposti dalla missione. All'interno del contenitore in alluminio verranno alloggiate le seguenti unità costituite da una o più schede di elettronica:

- **DAQ:** Data Acquisition. Consiste nell'insieme delle schede elettroniche che si trovano immediatamente a valle dei SiPM Il DAQ acquisisce e processa i segnali provenienti dai detector. Permette il controllo fine della regolazione della tensione di alimentazione dei SiPM in modo da equalizzare i guadagni e compensare le variazioni di temperatura;

- Concentratore: il Concentratore gestisce i trigger di alto livello (cioè deve supportare

la funzionalità di costruzione dell'evento globale in funzione delle caratteristiche del

segnale prodotto da uno o più sensori (SiPM) dei vari sottosistemi (UP e DOWN Pixel e

ACS). Il concentratore deve prevedere la capacità di comunicazione con la piattaforma

(attraverso un protocollo di comunicazione su bus SerDes), nonché di generare il flusso

di dati di downlink ed essere in grado di ricevere ed interpretare comandi in uplink

inviati dal segmento terra;

- **PS:** Power Supply. Questo sistema regola l'alimentazione (60 V 67.2 V non regolata) fornita dalla piattaforma al fine di ricavare le sia tensioni necessarie al funzionamento dei SiPM e dei PIPS sia quelle più basse e stabilizzate per l'alimentazione delle schede di elettronica. Il sistema di alimentazione deve essere opportunamente ridondato e deve essere capace di generare segnali di stato, di misurare le correnti assorbite sui vari rami della rete e di rispondere a tutti gli stati di funzionamento interpretando e producendo segnali utili all'implementazione di una logica di sicurezza del P/L;

- Backplane: Il backplane è il sistema che distribuisce le tensioni alle varie schede in uso

e che viene utilizzato per l'interconnessione di tutte le schede DAQ e concentratore. Esso

costituisce l'interfaccia elettrica verso il satellite.

## 4.1.3. EH o External Harness

La EH (External Harness) è l'insieme di cavi che realizzano la connessione elettrica tra la DU e la EU.

La sua progettazione e realizzazione deve rispondere ai principali requisiti dettati dalla missione: il numero di cavi e connessioni deve essere sufficiente a soddisfare tutte le interconnessioni elettriche richieste a livello di segnale, tensioni di alimentazione, segnali logici di controllo. L'EH deve essere in grado di operare all'interno dei parametri ambientali dell'orbita di riferimento per tutta la durata della missione, di sopportare i carichi statici e dinamici attesi nella fase di lancio e rispettare i vari budget di missione. Viene richiesto un sistema di stress release per i fissaggi meccanici.

## 4.2. Fornitura inerente EU-TEL

Oggetto di questa fornitura è l'elettronica di acquisizione dati e gestione EU-TEL. Sono previsti due piani di sviluppo:

Piano A: utilizzando ASIC sviluppati da INFN Torino

Piano B: usando ASIC Citiroc

Entrambe le forniture di ASIC sono escluse dal presente capitolato tecnico.

I due piani sono in parte sovrapponibili nella descrizione, sebbene si richieda la progettazione e la produzione di tutte le schede necessarie all'attuazione di entrambe le alternative. Maggiori dettagli riguardo la fornitura sono disponibili nella sezione 5.6.

# 5. Dettagli fornitura

La fornitura oggetto del presente capitolato tecnico riguarda attività di progettazione, ottimizzazione e ingegnerizzazione finalizzate allo sviluppo e alla realizzazione di un prototipo in scala, del SM, EM e FM del P/L Crystal Eye, nonchè della scheda di controllo EU-TEL. In particolare, le attività riguarderanno:

- progettazione, realizzazione e assemblaggio dei sub-detector di Crystal Eye (Up e DOWN Pixel e ACS) comprensivi delle SiPM-board e di tutte le necessarie infrastrutture meccaniche di supporto, sia per il prototipo che per i vari modelli;

- progettazione, realizzazione e assemblaggio dell'EU e dell'EH di Crystal Eye per il prototipo e i vari modelli;

- test di qualifica spaziale ai quali parteciperà anche personale GSSI;

- assemblaggio finale del P/L Crystal Eye;

- progettazione, realizzazione e assemblaggio del sistema di controllo EU-TEL

Nelle seguenti sottosezioni vengono descritti nel dettaglio i tre sottosistemi (Up e Down Pixel e ACS) che costituiscono il detector Crystal Eye. Maggiori dettagli sui fotosensori SiPM utilizzati nel detector vengono forniti nella sezione 6.

## 5.1. UP Pixel

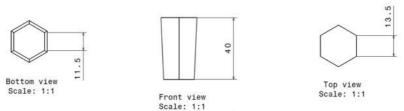

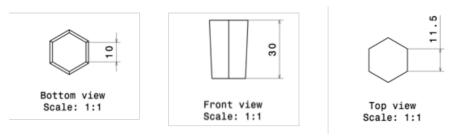

I pixel UP del Crystal Eye sono tronchi di piramide a base esagonale. L'altezza compresa fra 3 e 4 cm è ottimizzata per la rivelazione di raggi gamma di energia inferiore a 1 MeV.

Figura 4 Messa in tavola di un UP pixel del disegno di base.

Nella Figura 4 sono utilizzate le dimensioni di un UP pixel utilizzato nel disegno di base di Crystal Eye. Nel corso di questo progetto è prevista l'interazione fra l'aggiudicatario della gara e il personale GSSI al fine di ottimizzare le dimensioni del pixel per massimizzare le performance di rivelazione nel rispetto dei vincoli imposti dalla piattaforma.

Il materiale di cui saranno composti gli UP pixels è il GAGG-F, un cristallo scintillatore senza radioattività interna, vedi Tabella 1. Il trattamento superficiale previsto per gli UP pixel è a superfici lucidate ricoperte da Enhanced Specular Reflector (ESR). Ciascun cristallo dovrà essere otticamente isolato dai vicini e inserito in un alloggiamento meccanico a tenuta di luce.

Tabella 1 Principali caratteristiche dei diversi tipi di GAGG prodotti da Epic Crystal

|                             | GAGG-F          | GAGG-T          | GAGG-HL         | Unit              |

|-----------------------------|-----------------|-----------------|-----------------|-------------------|

| Density                     | 6.6             | 6.6             | 6.6             | g/cm <sup>3</sup> |

| Hardness                    | 8               | 8               | 8               | mohs              |

| Refractive Index            | 1.91            | 1.91            | 1.91            | 1                 |

| Light Output                | 30,000          | 42,000          | 54,000          | ph/MeV            |

| Energy Resolution           | 7%              | 6%              | 5%              | 5x5x5 mm@662KeV   |

| Decay Constant              | 50              | 90              | 150             | ns                |

| Wavelength of Emission Peak | 520             | 530             | 530             | nm                |

| Radiation Resistance        | 10 <sup>7</sup> | 10 <sup>7</sup> | 10 <sup>7</sup> | rad               |

| Hygroscopic                 | no              | no              | no              | 1                 |

| Self-radiation              | no              | no              | no              | 1                 |

|                             |                 |                 |                 |                   |

## 5.2. DOWN Pixel

I pixel DOWN del Crystal Eye sono tronchi di piramide a base esagonale. L'altezza compresa fra 3 e 4 cm e la posizione sono ottimizzate per la rivelazione di raggi gamma di energia superiore a 1 MeV.

Figura 5 Messa in tavola di un DOWN pixel del disegno di base.

Nella Figura 5 sono utilizzate le dimensioni di un DOWN pixel utilizzato nel disegno di base di Crystal Eye. Nel corso di questo progetto è prevista l'interazione fra l'aggiudicatario della gara e il personale GSSI al fine di ottimizzare le dimensioni del pixel per massimizzare le performance di rivelazione nel rispetto dei vincoli imposti dalla piattaforma.

Il materiale di cui saranno composti gli UP pixels è il LYSO, un cristallo scintillatore, vedi Tabella 1. Il trattamento superficiale previsto per i DOWN pixel è a superfici lucidate ricoperte da Enhanced Specular Reflector (ESR). Ciascun cristallo dovrà essere otticamente isolato dai vicini e inserito in un alloggiamento meccanico a tenuta di luce.

Tabella 2 Principali caratteristiche de LYSO prodotto da Epic Crystal

|                             | LYSO(Ce)            | Unit              |

|-----------------------------|---------------------|-------------------|

| Density                     | 7.25                | g/cm <sup>3</sup> |

| Wavelength of Emission Peak | 420                 | nm                |

| Light Output                | 30,000              | ph/MeV            |

| Decay Constant              | 40                  | ns                |

| Anti-radiation              | 1 x 10 <sup>8</sup> | rad               |

| Refractive Index            | 1.82                | I                 |

| Hardness                    | 5.80                | mohs              |

| Hygroscopic                 | no                  | 1                 |

| Cleavage                    | no                  | 1                 |

|                             |                     |                   |

## **5.3. ACS**

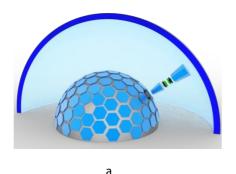

Il sistema di anticoincidenza (ACS) consiste nell'utilizzo di scintillatore plastico per racchiudere i pixel di Crystal Eye. Lo scopo è duplice: localizzare la componente di raggi gamma di più bassa energia (10-40 keV) e etichettare le particelle cariche che attraversano il Crystal Eye.

L'ACS si compone principalmente di due parti: TOP-ACS e BOTTOM-ACS. Il design del sistema di anticoincidenza va ottimizzato in termini di capacità di localizzazione e ermeticità (cioè minimizzando gli spazi morti).

Attualmente per la TOP-ACS sono presi in considerazione due ipotesi: una a calotta sferica Figura 6a, l'altra a tile esagonali Figura 6b. Lo spessore della TOP-ACS dovrà essere compreso fra 5 e 7 mm.

Nel primo caso, Figura 6a, la calotta sferica è costituita da tile singole come nel secondo caso meccanicamente accoppiate fra loro dalla ditta che produce lo scintillatore in modo da presentarsi di fatto come un unico blocco. Le tile sono otticamente isolate fra loro grazie a un trattamento effettuato dalla ditta produttrice dello scintillatore e sono singolarmente lette da SiPM posti lungo la superficie della calotta.

b

Figura 6 a) TOP-ACS a calotta sferica, b) TOP-ACS a tile.

La BOTTOM-ACS è invece costituita da un disco di scintillatore plastico che andrà a chiusura inferiore del detector. Durante il progetto si valuterà se realizzare un disco unico o diviso in spicchi.

## 5.4. SiPM Board

Tutti i subdetector appena descritti si basano sull'utilizzo di materiali scintillanti, cioè che emettono luce in proporzione all'energia depositata al loro interno dalla particella che li attraversa. E' quindi indispensabile avere un'ottima lettura della luce emessa. A questo scopo ciascuno scintillatore sarà letto da SiPM. Le schede che alloggeranno i SiPM dovranno essere realizzate in PMMA, come da buona pratica per elettronica in applicazioni spaziali. Forma, numero di SiPM per board, interconnessioni, alloggiamento meccanico saranno definite in fase di sviluppo. Ogni board SiPM dovrà contenere un sensore analogico di temperatura. Il connettore verso l'EU sarà di tipo microcoassiale.

Ciascuna SiPM board dovrà essere adattabile ai footprint dei SiPM Hamamatsu e di quelli FBK. I footprint dei SiPM saranno forniti al kick off meeting.

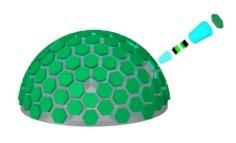

Figura 7 Schemi rappresentativi di SiPM board di lettura dei cristalli (a) e dell'ACS (b)

I cristalli prevedono 3 canali di lettura più un canale di ridondanza, mentre ciascuna tile dell'ACS prevede 2 canali di lettura più uno ridondato. Per ciascun pixel i canali sono:

- LE-c, il canale Low Energy di ciascun cristallo composto da due SiPM 6x6 letti separatamente

- ME-c, il canale Medium Energy di ciascun cristallo composto da una coppia di SiPM 3x3 in or-analogico

- Red-c, il canale di ridondanza dei cristalli composto da una coppia di SiPM 3x3 in oranalogico

- ACS-1, il primo canale di lettura di ciascuna tile ACS-TOP dato da una coppia di SiPM 3x3 in or-analogico

- ACS-2, il secondo canale di lettura di ciascuna tile ACS-TOP dato una coppia di SiPM 3x3 in or-analogico

- Red-ACS, il canale di ridondanza ACS dato da una coppia di SiPM 3x3 in or-analogico

- ACS-bottom, i SiPM utilizzati saranno i 6x6, il numero effettivo di canali di lettura sarà stabilito in corso del progetto

Ogni pixel completo (composto da ACS-TOP, UP e DOWN Pixel) avrà quindi in totale 8 canali di lettura e due di ridondanza.

Le quantità indicate in sezione 6 sono da intendersi per la realizzazione di ciascun modello di P/L (EM e FM), le quantità necessarie al prototipo saranno indicate con la flag "-p".

Sarà richiesto l'approvvigionamento di una contingenza del 10% per garantire la sostituzione in caso di malfunzionamenti

o fuori specifica.

# 5.5. Electronics Unit (EU)

#### L' EU sarà composta da:

- A. Un numero adeguato di schede di DAQ, basato su chip CITIROC o RADIOROC, per il readout di dei canali di lettura delle SiPM board. La scheda DAQ, indirizzabile da una scheda concentratore, deve gestire il chip CITIROC/RADIOROC, effettuare la sequenza di lettura, generare i trigger di colonna, secondo una serie di maschere di trigger programmabili in modo da ridurre gli 8 segnali di trigger a 1 solo segnale di trigger per pixel. La DAQ deve essere inoltre in grado di ricevere un trigger globale di satellite che causa la lettura di tutti i canali, inclusi quelli che non hanno triggerato. La scheda deve fornire per ogni canale l'informazione di trigger (HIT), carica HG, carica LG, timing e i dati di housekeeping (timestamp, temperatura, posizione, orientamento)

- B. Una variante della precedente scheda, ma con le medesime caratteristiche tecniche, per la lettura della bottom ACS

- C. Una scheda trigger globale, in grado di generare un trigger di satellite a fronte dei trigger di colonna (trigger generati dai pixel)

- D. Una scheda concentratore in grado di leggere i segnali digitalizzati da (A) e (B) a fronte di un trigger globale generato da (C). Il concentratore deve essere in grado di comunicare con la onboard CPU tramite bus seriale ad alta velocità (SERDES) e per lo slow control tramite CAN BUS

- E. Sistema di ridondanza

- F. Backplane

- G. Alimentatori di HV per i SiPM e relativa scheda di gestione

- H. Alimentatori in grado di fornire le low-voltage necessarie a tutte le schede dell'EU

# 5.5.1. DAQ board (A)

Ogni scheda DAQ di read-out dei SiPM, deve leggere 8 pixel, quindi, queste schede dovranno essere dei sistemi digitali con a bordo 2 CITIROC o 1 RADIOROC in modo che sia possibile leggere un

totale di 64 canali per ciascuna. Ogni DAQ R/O Board deve interfacciarsi con le SiPM board tramite uno o più connettori micro-coassiali.

Si richiede di non incrementare il numero di pixel per scheda per motivi di ridondanza. Sui 64 canali, i chip CITIROC o RADIOROC, forniscono 64 segnali di trigger indipendenti e due uscite multiplexate di energia (HG e LG). La scheda deve essere equipaggiata con un dispositivo FPGA riprogrammabile in grado di fornire in uscita 8 segnali di trigger a partire dai 64 segnali di ingresso. I segnali di trigger saranno uno per pixel e seguiranno uno schema di trigger codificato in molteplici maschere di trigger programmabili nel dispositivo. Oltre alle uscite di trigger l'FPGA deve essere in grado di convertire le uscite HG e LG di tutti gli ASIC, tramite ADC con una risoluzione di almeno 14 bit.

Il firmware nell'FPGA deve essere tale da gestire il sequencing dell'ASIC per effettuare l'operazione di lettura, e deve avere sufficiente memoria da immagazzinare un evento letto su tutti i 64 canali fino a che la scheda concentratore, non provvederà, tramite interfaccia seriale veloce (>50MHz), a rileggere l'intero evento e riarmare il sistema.

Il circuito di questa scheda deve essere progettato affinché l'alimentazione sia gestita solo tramite alimentatori lineari. Devono essere inoltre previsti sistemi per proteggere il dispositivo in caso di SEL. Il firmware deve essere aggiornabile dalla scheda concentratore.

Ciascuna DAQ deve anche ospitare un convertitore ADC a 24 canali, in grado di convertire le tensioni prodotte dai sensori di temperature. E' richiesta un'accuratezza di 0.1°C

E' necessario che i banchi di trigger degli ASIC CITIROC/RADIOROC siano alimentati a 1.8 V per ridurre il cross-talk tra i canali.

Le schede necessarie nel sistema saranno da 14 a 23 a seconda del numero di pixel presenti nel modello finale (min 112, max 181) dopo la fase di ottimizzazione iniziale del design.

# 5.5.2. Trigger board (C)

La scheda di trigger deve raggruppare i segnali di trigger provenienti da tutti i pixel, e tramite un algoritmo topologico con maschera NxN decide se generare un trigger di satellite o no. Il dispositivo deve generare il trigger nel minor tempo possibile (<50ns). Questo tempo è dettato dal peaking time interno al chip Citiroc.

L'FPGS alla base di questa scheda è critica per il timing del satellite. Deve essere scelto un dispositivo di ultima generazione e di grande area in modo da minimizzare il tempo di elaborazione del trigger. La scheda può utilizzare alimentatori switching in quanto non opera su segnali analogici.

# 5.5.3. Concentratore (D)

La scheda, a fronte di un segnale di trigger da parte della trigger board (C) inizia la procedura di lettura dei dati convertiti dalle schede DAQ (A e B). La scheda concentratore deve essere equipaggiata con una interfaccia SPI lenta per la configurazione delle schede di front-end e di trigger e di un'interfaccia SPI veloce (LVDS) per la lettura dei dati scientifici dalle schede di front-end. Una volta acquisiti dalla scheda concentratore, i segnali digitalizzati dalle schede di front-end devono

Una volta acquisiti dalla scheda concentratore, i segnali digitalizzati dalle schede di front-end devono essere organizzati in eventi, etichettati con timestamp tramite il tempo assoluto GPS (con risoluzione di 10ns) e processati.

Si chiede di utilizzare una struttura mista FPGA+CPU o SoC (Zynq Ultrascale+). I dati verranno acquisiti dall'FPGA e organizzati in pacchetti. La CPU si occuperà di pre-processare a bordo gli eventi, formattarli in modo che siano comprensibili dalla DPCU del satellite e inviati a terra tramite link seriale veloce (GTH/P). Gli algoritmi di processamento da eseguire sulla CPU saranno definiti in itinere.

Il concentratore deve avere almeno 2 Gbyte di memoria DDR4 con ECC, e deve essere progettato in modo da leggere in parallelo tutte le schede (A e B).

Sia il firmware FPGA sia quello della CPU (o in alternativa il firmware del SoC) devono essere riprogrammabili da terra, quantomeno la parte di firmware che si occupa del datapath e dell'elaborazione anche durante la missione.

Devono essere presenti sempre due copie di firmware in modo da poter gestire in modo sicuro la procedura di firmware upgrade

Il concentratore, oltre alla lettura dei dati scientifici, il loro processamento e l'invio a terra deve:

- Gestire la comunicazione (slow-control/telemetria) verso il satellite tramite can bus

- Gestire la configurazione delle DAQ e della trigger board

- Gestire il firmware upgrade di se stesso

- Gestire il firmware upgrade di front-end board e trigger board o in alternativa distribuire il firmware in modo dinamico dal concentratore

- Gestire e monitorare le HV del sistema

- Provvedere a un adeguato algoritmo di compensazione del guadagno dei SiPM variando sia le tensioni di HV che i DAC di correzione di tutti i CITIROC/RADIOROC

- Monitora l'alimentatore del sistema e tutti i rami derivati dall'alimentazione primaria

Il concentratore deve essere equipaggiato con un sistema operativo UNIX-like.

Oltre al bus CAN e al bus SERDES, utilizzati in volo, il concentratore deve prevedere la possibilità di eseguire tutte le operazioni tramite interfaccia Ethernet, su protocollo TCP/IP, per tutte le operazioni di testing e sviluppo a terra.

Deve essere fornita una libreria C++ per la configurazione e il readout (compatibile con LINUX e WINDOWS) e un client grafico (solo WINDOWS) per l'operabilità a terra. Il client e la libreria devono permettere la configurazione, a partire da un file di configurazione testuale, di tutte le impostazioni delle schede di front-end, trigger, e concentratore. Inoltre devono prevedere la lettura di tutti i canali simultaneamente del satellite. Il solo client WINDOWS deve poter mostrare immagini in tempo reale, utilizzando le distribuzioni spaziali dell'energia e gli spettri di energia di tutti i canali. Il client deve anche permettere di controllare l'alimentazione e monitorare lo slow control (temperature).

Infine il concentratore deve fornire un segnale di ALERT rapido verso terra, entro massimo 2 secondi dall'evento, a fronte di una particolare condizione (TRIGGER+analisi dell'evento in tempo reale), tramite un segnale di telecomando al satellite.

# 5.5.4. Sistema di ridondanza (E)

La missione non richiede l'uso di componenti space grade. In ogni caso, nella scelta dei componenti, in ragione anche della fattibilità economica è opportuno scegliere nell'ordine

- Componenti Automotive

- Componenti Industriali

Non sono ammessi componenti commercial. Il range di temperatura di funzionamento deve essere almeno -40 +80 °C.

Tutti i componenti passivi devono essere almeno Automotive.

Tali componenti, non essendo qualificati spazio, non possono garantire un livello alto di affidabilità pertanto è necessario rimuovere tutti i single point failure.

Di seguito la minima strategia di ridondanza proposta al fine di mitigare la rottura di eventuali parti del sistema durante la missione:

- 1. Ogni SiPM board ha un canale di ridondanza (Red-c e Red-ACS).

- 2. I canali ridondati delle SiPM board vanno su DAQ di ridondanza (DAQ-red)

- 3. Oltre alla trigger board primaria ce ne sarà una di ridondanza(trigger board-red)

- 4. Oltre al concentratore primario ce ne sarà uno di ridondanza (concentratore-red)

Le schede ridondate (DAQ-red), per quanto detto nel punto 1, saranno quindi 3xN/64 (dove N è il numero di pixel della configurazione finale del detector). Per quanto detto nel punto 3, ogni DAQ (A e B) dovrà provvedere alla duplicazione dei dati. Dovrà quindi avere:

- 2 interfacce trigger in uscita (ciascuna con 8 trigger) à una per ciascuna trigger board

- o 2 spi di configurazione à una per ciascun concentratore

- o 2 spi di lettura à una per ciascun concentratore

- o 2 interfacce di riconfigurazione à una per ciascun concentratore

- o 2 ingressi di trigger di satellite à una per ciascuna trigger board

Infine la DAQ bottom ACS (B) deve essere duplicata mettendo 16 canali sulla trigger board primaria e 16 su quella ridondata.

Le trigger board (primaria e red) ricevono ciascuna una copia degli 8 trigger dalla schede DAQ e generano indipendentemente un segnale di trigger di satellite.

Per ragioni di sicurezza, il trigger di satellite deve avere una connessione a stella, con un pin di uscita dedicato per ogni scheda DAQ in modo che la rottura di una di queste non possa portare al blocco totale del trigger.

Le seguenti interfacce di ciascuna trigger board devono essere duplicate:

o 2 spi di configurazione à ogni interfaccia è connessa a un differente concentratore

Ogni scheda concentratore (primaria e red) è connessa a tutte le 24 DAQ tramite:

- o 1 interfaccia SPI di configurazione

- 1 interfaccia SPI di lettura dati veloce (LVDS)

- 1 porta di riconfigurazione firmware

Inoltre viene connessa a ciascuna delle due trigger board (primaria e red) tramite:

- o 1 interfaccia SPI di configurazione

- o 1 trigger di satellite

- o 1 porta di riconfigurazione firmware

Verso il satellite, ciascun concentratore (primario e red) sarà fornito di un'interfaccia CAN BUS e SERDES indipendente.

In caso di faliure di qualunque dei sistemi deve essere possibile disattivare l'alimentazione della parte compromessa e il sistema deve proseguire con le parti rimaste o di backup. In paricolare, in caso di:

- Guasto di un SiPM à deve essere possibile spegnere tutto il gruppo di HV a cui il SiPM è connesso

- Guasto a uno o più canali della scheda front-end à a livello di scheda front-end tali canali devono essere esclusi dal trigger

- Guasto a una scheda di front-endà La scheda deve essere spenta dal power supply, il trigger deve mascherare i trigger di quella board, lo schema di trigger riprogrammato per escludere la scheda e il concentratore deve ignorare dati casuali provenienti da tale scheda. Il sistema perde 1/23 della calotta sferica a ogni rottura di front-end

- Guasto di una trigger boardà la scheda viene spenta e si accende la trigger board-red. Le DAQ vengono informate dal concentratore di utilizzare la trigger board-red

- Guasto al concentratore à il concentratore primario viene spento e si accende il concentratore-red. Le schede vengono informate tramite telecomando che il concentratore primario è spento e tutto il controllo passa al concentratore-red

- La DAQ bottom ACS si guasta à la DAQ bottom ACS primaria viene spenta e si passa a quella ridondata

# 5.5.5. Payload Power Supply o (PS)

Gli alimentatori regolano la tensione fornita dalla piattaforma per generare le tensioni (HV) necessarie al funzionamento dei SiPM e quelle (LV) per il funzionamento delle schede di elettronica. Tutte le HV necessarie al corretto funzionamento del P/L devono essere generate linearmente a partire dalla linea 60 V - 67.2 V servita dalla potenziale piattaforma. Ciascun sottosistema (UP e DOWN pixel e ACS) viene servito da un sistema di alimentazione dedicato. Tutte le tensioni generate e messe al servizio dell'operatività del P/L dovranno essere fornite in modo indipendente (ogni scheda deve poter essere alimentata in modo esclusivo) e dovranno essere ridondate.

Il sistema di alimentazione dovrà necessariamente generare una tensione (HV) variabile limitata a 65 V e dovrà essere in grado di generare i seguenti livelli di tensione (LV) che fisseranno la configurazione delle schede di funzionamento del P/L Crystal Eye:

- Linea A, Output 5 V, Corrente max 10 A

- Linea B, Output 3.7 V, Corrente max 5 A

- Linea C, Output 2.2 V, Corrente max 1 A

- Linea D, Output 1.0 V, Corrente max 2 A, picco 10 A

Il livello di tensione HV deve essere consistente con le caratteristiche del fotosensore utilizzato per la lettura di luce di scintillazione di ciascun sottosistema. L'efficienza di conversione delle tensioni deve essere uguale o superiore a 85 %.

È necessario l'utilizzo di un survoltore per operare uno o più sottosistemi del P/L.

Tutte le tensioni dovranno essere monitorate con una risoluzione migliore o uguale a 10 mV, mentre si richiede una risoluzione migliore o uguale a 1 mA per la misura della corrente. Il sistema dovrà essere in grado di reagire in tempi brevi (entro 10 ms) ad eventuali latchup e cortocircuiti e tagliare immediatamente le alimentazioni in modo da mitigare il rischio di evento di failure globale in cui le operazioni del P/L vengono irrimediabilmente compromesse.

Misura e controllo dei parametri devono essere trasmessi indipendentemente verso la piattaforma (CanBus) e verso la scheda di raccolta dati scientifici (concentratore) al fine di avere un riferimento ai parametri di funzionamento durante la fase di analisi dati.

Il ripple di tutti i convertitori non deve eccedere i 10 mV, ad esclusione del generatore di tensione per i SiPM in cui la richiesta è più stringente (< 2 mV).

I SiPM potranno essere alimentati a gruppi con una tensione regolabile e limitata a 65 V. Ogni SiPM sarà provvisto di limitatore in corrente a 100 μA. Dovrà essere previsto un sistema di retroazione fra le tensioni di alimentazione dei SiPM in funzione della temperatura misurata al fine di provvedere alla compensazione e stabilizzazione del guadagno in tempo reale.

# 5.5.6. Backplane

Il backplane sarà una scheda passiva per la distribuzione dei segnali e delle alimentazioni. Forma e dimensioni verranno fornite dal committente al soggetto aggiudicatario della gara. In fase di progettazione, viene richiesta la migliore soluzione ottenibile in termini di resistenza e affidabilità meccanica (con speciale riguardo alle fasi di lancio) e di connessione con le schede DAQ e concentratore.

## **5.6. EU-TEL**

Sono previsti due piani di sviluppo:

- Piano A utilizzando ASIC sviluppati da INFN Torino

- Piano B usando ASIC Citiroc

I due piani sono in parte sovrapponibili nella descrizione, sebbene si richieda la progettazione e la produzione di tutte le schede necessarie all'attuazione di entrambi i piani.

#### PIANO A

Il sistema di lettura EU-TEL sarà composto da quattro schede secondo l'elenco che segue, tra queste soltanto le schede C. e D. sono oggetto della presente fornitura. Le schede A. e B. sono indicate nell'elenco solo a titolo esplicativo per la definizione delle caratteristiche e funzionalità delle schede oggetto della fornitura (vedi schema logico pagina seguente).

- A. Scheda del rivelatore SiPM (esclusa dalla presente fornitura)

- B. Scheda ASIC (esclusa dalla presente fornitura)

- C. Scheda FPGA del Front End

- D. Concentratore di Dati

POWER MANAGMENT AND CONTROL

Figura 8 Principali funzioni della scheda DAQ e dell'ASIC stesso

Prima di analizzare la reale distribuzione hardware degli elementi, presentiamo uno schema logico del Sistema EU-TEL.

**SCHEDA SIPM:** Su questa scheda verranno installati 640 SiPM oltre a diversi sensori di temperatura analogici.

**SCHEDA ASIC**: La scheda ASIC (presente solo nel caso del Piano A) contiene l'ASIC progettato da INFN Torino, insieme ai loro regolatori LDO. La scheda funziona come passaggio per HV e sensori di temperatura.

Nel diagramma di sopra sono rappresentate le principali funzioni della scheda ASIC e dell'ASIC stesso.

#### In sintesi:

Ogni ASIC produce un Trigger L0, che significa rilevare almeno un pixel oltre la soglia (o

forse Torino implementerà una sorta di trigger di topologia o di maggioranza). Il trigger L0

produce una HITMAP e un segnale di trigger out per informare l'FPGA che un evento può

essere convertito;

• La conversione della memoria analogica avviene su richiesta di digitalizzazione dalla scheda FPGA.

Le specifiche finali dell'ASIC sono in fase di definizione, così come il pinout. Sicuramente le interfacce elettriche tra ASIC e FPGA sono tutte LVDS con bit rate di 833 Mbit/s per lane in DDR.

**SCHEDA FPGA FRONT-END**: La scheda FPGA contiene FPGA per leggere gli ASIC e funge da interfaccia con il CONCENTRATORE DI DATI. Contiene anche i regolatori LDO per l'FPGA, l'ADC per convertire i segnali ANALOGICI dei sensori di temperatura.

Le principali funzioni della scheda FPGA sono identificate sopra.

#### In sintesi:

- Trigger L1: prende gli output di trigger da tutti gli ASIC e genera un trigger globale (OR tra

tutti gli output di trigger ASIC o richiesta di lettura) per richiedere a tutti gli ASIC di fornire

la HITMAP. In base alle HITMAP di tutti gli ASIC, la logica decide se avviare la conversione

A-D su ASIC e inviare i dati al CONCENTRATORE;

- Trasmettitore di dati: prende i dati da tutti i moduli di lettura ASIC (de-serializer) e prepara un EVENTO RAW da inviare al concentratore di dati;

- Configurazione ASIC: riceve il flusso di bit di configurazione ASIC tramite controllo lento e

controlla la configurazione SPI ASIC per configurare tutti gli ASIC in base al flusso di bit

fornito dal concentratore di dati;

- ADC di temperatura: converte in valori RAW la temperatura dal sensore analogico e li condivide con l'interfaccia HK del concentratore;

- Gestione della scheda (HK): monitora le temperature, le tensioni e le correnti della scheda FPGA. Fornisce, canale per canale, il monitoraggio del contatore di frequenza insieme al contatore di frequenza di sistema e alla misurazione del tempo morto totale.

**CONCENTRATORE DI DATI**: Il concentratore di dati è una scheda mista FPGA+CPU, o meglio SoC (Zynq Ultrascale +) il quale combina un FPGA con un processore ARM-64 quad core. Contiene anche SERDES e interfaccia CAN bus per il DCPU Thales e l'interfaccia con HV. Fornirà interfacce Scientifiche e di Slow-Control alla scheda FPGA. Le attività possono essere suddivise in attività FPGA e CPU.

### ATTIVITÀ FPGA

- Ricevere dati dalla scheda FPGA, organizzarli in eventi (costruttore di eventi), fornirli con un timestamp con una precisione di 10 ns e fornire un ampio buffer per memorizzare gli eventi in DDR in attesa di essere trattati dagli algoritmi CPU.

- Assegnare il timestamp dell'evento utilizzando il GPS + TDC

- Fornire una coda di output in DDR al SERDES per gli eventi in attesa di essere trasferiti al SERDES e quindi alla stazione di terra tramite DCPU THALES

- Fornire un'interfaccia hardware al BUS CAN del satellite mostrando un'interfaccia slave CAN al Zynq

- Trasferire i registri di configurazione (incluso il flusso di bit) tramite SPI alla scheda FPGA.

• Implementare l'interfaccia SPI HK con scheda ASIC, scheda HV, e scheda LV (modulo di alimentazione)

## ATTIVITÀ CPU

- Elaborare eventi, con algoritmi personalizzati definiti dall'utente. Devono essere supportati C++ e Python.

- Eseguire il ciclo di compensazione HV ottenendo temperature dalla scheda FPGA, calibrare i valori grezzi e controllare l'HV sulla gestione dell'alimentazione.

- Monitorare le schede FPGA, concentratore e PSU, HK e generare allarmi.

- Decodificare il file di configurazione del sistema fornito dalla stazione di terra o dal pc di bordo.

- Configurare i parametri di elaborazione sulla scheda FPGA e sull'algoritmo utente utilizzando il file di configurazione del sistema o lo script fornito dalla stazione di terra.

- Gestire i download del firmware della scheda FPGA.

- Gestire l'aggiornamento del firmware FPGA e CONCENTRATORE.

- Gestire l'aggiornamento dell'algoritmo software utente.

- Monitorare il rilevatore di errori di configurazione sia nel concentratore che nella scheda FPGA.

- Gestire l'uso totale dei dati e limitare la larghezza di banda al giorno.

## Scheda FPGA di front-end (C.)

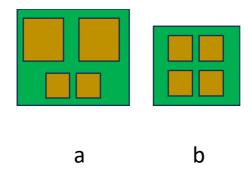

La scheda front-end FPGA è composta da un modulo plug-in in grado di leggere 5/8 ASIC (a seconda della variante di montaggio). La scheda presenta due connettori, uno verso il backplane e uno verso la scheda ASIC, che è collegata all'FPGA tramite cavi micro-coassiali intrecciati.

La decisione di separare la scheda ASIC dalla scheda FPGA è stata presa per i seguenti motivi:

- Dissipazione di potenza: La scheda FPGA genera calore che potrebbe influenzare gli ASIC e i sensori.

- Radiazione: La scheda FPGA è inserita all'interno del vassoio elettronico, dove sarà schermata dalle radiazioni spaziali ed esposta solo ai sensori e alla scheda ASIC.

Si richiede di scegliere un dispositivo FPGA di dimensione e velocità adeguata per:

- Gestire le attività di lettura, configurazione del trigger, pre-elaborazione (analisi delle HITMAP) e trasferimento dei dati al concentratore.

- Gestire l'elevata velocità di lettura degli ASIC (fino a 880 Mbit/s per lane senza l'uso della codifica Manchester), che richiede una velocità I/O ad alte prestazioni.

L'alimentazione per l'intera scheda deve essere post-regolata utilizzando LDO (regolatori a bassa caduta) a basso rumore. Interruttori automatici con allarmi devono essere posti a valle degli LDO per riavviare la scheda se viene rilevato un latch-up (SEL) in una qualsiasi dei ring di delle alimentazioni.

Al fine di ridurre la dissipazione di potenza su LDO, la scheda di alimentazione deve fornire rails separati per ogni alimentazione con un margine di tensione limitato per consentire la caduta di LDO e la caduta di tensione di distribuzione.

Il firmware della scheda FPGA deve essere aggiornabile da terra tramite concentratore

Per leggere l'intero piano focale, sono necessarie due schede FPGA di front-end, che per ragioni di ridondanza, devono essere interamente duplicate.

Oltre a leggere gli ASIC, la scheda gestisce anche il controllo lento. Deve essere equipaggiata con un ADC a 16 canali per leggere i sensori di temperatura analogici posizionati sotto tutte le tile di SiPM.

Tali sensori devono anche funzionare durante la procedura di aneling in quanto forniscono l'informazione di temperatura al sistema di controllo PID del sistema di riscaldamento dei SiPM

## Scheda Concentratore (D.)

La scheda, a fronte di un segnale di trigger da parte dell'FPGA di front-end inizia la procedura di lettura dei dati convertiti dalle schede front La scheda concentratore deve essere equipaggiata con una interfaccia SPI lenta per la configurazione delle schede di front-end e di trigger e di un'interfaccia SPI veloce (LVDS x8 canali dati) per la lettura dei dati scientifici dalle schede di front-end.

Una volta acquisiti dalla scheda concentratore, i segnali digitalizzati dalle schede di front-end devono essere organizzati in eventi, timestampati tramite il tempo assoluto GPS (con risoluzione di 10ns) e processati.

Si chiede di utilizzare una struttura mista FPGA+CPU o SoC (Zynq Ultrascale+). I dati verranno acquisiti dall'FPGA e organizzati in pacchetti. La CPU si occuperà di pre-processare a bordo gli eventi, formattali in modo che siano comprensibili dalla DCPU del satellite e inviati a terra tramite link seriale veloce (GTH/P). Gli algoritmi di processamento da eseguire sulla CPU saranno definiti ad-itinerem.

Il concentratore deve avere almeno 2 Gbyte di memoria DDR4 con ECC, e deve essere progettato in modo da leggere in parallelo tutte e due le schede di front-end.

Inoltre il concentratore deve fungere a distributore del trigger. Deve infatti ricevere il trigger delle due schede di front-end, fare l'OR, e inoltrarlo alle due schede in modo da creare un trigger di satellite.

Sia il firmware FPGA che CPU (o in alternativa il firmware del SoC) deve essere riprogrammabile da terra, quantomeno la parte di firmware che si occupa del datapath e dell'elaborazione anche durante la missione.

Devono essere presenti sempre due copie di firmware in modo da porter gestire in modo sicuro la procedura di firmware upgrade

Il concentratore, oltre alla lettura dei dati scientifici, il loro processamento e l'invio a terra deve:

- Gestire la comunicazione (slow-control/telemetria) verso il satellite tramite can bus

- Gestire la configurazione delle schede di front-end

- Gestire il firmware upgrade di se stesso

- Gestire il firmware upgrade delle front-end board o in alternativa distribuire il firmware in modo dinamico dal concentratore

- Gestire e monitorare le HV del sistema

- Provvedere a un adeguato algoritmo di compensazione del guadagno dei SiPM variando le tensioni di HV

- Monitora l'alimentatore del sistema e tutti i rami derivati dall'alimentazione primaria

Il concentratore deve essere equipaggiato con un sistema operativo UNIX like. Deve essere fornito supporto a C++ e Python.

Si richiede di fornire un SDK per poter sviluppare in modo autonomo il firmware di elaborazione.

Oltre al bus CAN e al bus SERDES (>3Gbps), utilizzati in volo, il concentratore deve prevedere la possibilità di eseguire tutte le operazioni tramite interfaccia ethernet, su protocollo TCP/IP, per tutte le operazioni di testing e sviluppo a terra.

Deve essere fornito una libreria C++ per la configurazione e il readout (compatibile con LINUX e WINDOWS) per l'operabilità a terra. Il client e la libreria devono permettere la configurazione, a partire da un file di configurazione testuale, di tutte le impostazioni delle schede di front-end, degli ASIC, degli schemi di trigger trigger, e del concentratore. Inoltre devono prevedere la lettura di tutti i canali simultaneamente del satellite.

Il client deve anche permettere di controllare l'alimentazione e monitorare lo slow control (temperature)

#### RIDONDANZA

La missione non richiede l'uso di componenti space grade. In ogni caso, nella scelta dei componenti, in ragione anche della fattibilità economica è opportuno scegliere nell'ordine

- Componenti Automotive

- Componenti Industriali

Non sono ammessi componenti commercial. Il range di temperatura di funzionamento deve essere almeno -40 +80 °C.

Tutti i componenti passivi devono essere almeno Automotive.

Tali componenti, non essendo qualificati spazio, non possono garantire un livello alto di affidabilità pertanto è necessario rimuovere tutti i single point failure

Di seguito la minima strategia di ridondanza proposta al fine di mitigare la rottura di eventuali parti del sistema durante la missione:

- Gli ASIC siano partizionati su due board: 5 ASIC saranno collegati all'FPGA di readout A e 5 all'FPGA B. I due FPGA devono essere totalmente indipendenti. È di fondamentale importanza che i due FPGA abbiano alimentazioni separate, regolatori di potenza e interfacce verso ASIC e CONCENTRATORI indipendenti. I sensori di temperatura dovrebbero essere divisi in gruppo A e B, leggendo ciascun gruppo da un FPGA diverso con ADC indipendente.

- Le due FPGA possono essere collegati insieme con una connessione orizzontale utilizzando un BUS con una sorta di resistori in serie per limitare la corrente (ad es. 100 R) e diodo di protezione da sovratensione o bus optoisolato. Questo BUS sarà necessario per implementare schemi di trigger L1, quei trigger si estendono oltre il bordo del singolo dispositivo FPGA.

- Ci sarà la possibilità da parte di THALES DCPU o concentratore di spegnere uno dei due FPGA se si verifica un evento irrecuperabile durante la missione.

- Le due FPGA si interfacciano con due concentratori DATI. Solo un concentratore di dati alla volta può essere alimentato. Predisporre un MUX che collega automaticamente ciascuna

FPGA al solo concentratore acceso. La gestione dell'alimentazione che attiva un determinato concentratore è controllata direttamente dalla stazione di terra tramite un comando remoto (da definire).

Tutte le interfacce tra il concentratore di dati e la scheda FPGA sono ridondanti. I dati scientifici, l'HK e il controllo lento, l'interfaccia di download del firmware sono tutti disponibili come porta A e B. Solo una porta alla volta deve essere attivata dal concentratore che è alimentato (in modo da non avere nessun consumo di energia aggiuntivo dal secondo concentratore inattivo).

I due concentratori devono avere un'interfaccia completamente ridondante con il satellite. Ognuno deve avere un SERDES e CAN BUS indipendente e il satellite si aspetterà e trasmetterà dati solo dalla/dalla porta che è effettivamente attivata dal controllo remoto.

In caso di faliure di qualunque dei sistemi deve essere possibile disattivare l'alimentazione della parte compromessa e il sistema deve proseguire con le parti rimaste o di backup.

In paricolare, in caso di:

- Guasto di un SiPM → deve essere possibile spegnere tutto il gruppo di HV a cui il SiPM è connesso

- Guasto a una scheda ASIC → se il consumo di corrente è eccessivo, la scheda ASIC deve essere spenta e il sistema funziona al 50%. Se possibile continuare con la scheda accesa, verranno esclusi da terra i canali danneggiati

- Guasto a una scheda FPGA (C) → se il consumo di corrente è eccessivo, la scheda FPGA deve essere spenta e il sistema funziona al 50%. Se possibile continuare con la scheda accesa, verranno esclusi da terra i canali danneggiati

- Guasto a un concentratore → il concentratore primario viene spento e si accende il concentratore di backup. Le schede vengono informate tramite telecomando che il concentratore primario è spento e tutto il controllo passa al concentratore secondario. EU-TEL deve poter continuare ad operare al 100% anche con il concentratore di backup

#### PIANO B

Il sistema di lettura EU-TEL sarà composto da tre schede secondo l'elenco che segue, tra queste soltanto le schede B. e C. sono oggetto della presente fornitura. La scheda A. è indicata nell'elenco solo a titolo esplicativo per la definizione delle caratteristiche e funzionalità delle schede oggetto della fornitura.

Il sistema di lettura EU-TEL sarà composto da tre schede:

- A. Scheda del rivelatore SiPM (esclusa dalla presente fornitura)

- B. Scheda ASIC + FPGA

- C. Concentratore di Dati

La scheda FPGA+ASIC deve avere caratteristiche differenti da quanto illustrato nel precedente paragrafo.

Utilizzando ASIC Citiroc, non sarà possibile la memorizzazione delle forme ma solo delle energie. La scheda deve quindi provvedere a implementare uno schema di trigger locale (a livello di scheda) e globale (a livello di concentratore). Deve quindi provvedere a fornire le misure di energia per tutti i canali.

Le schede di DAQ dovranno provvedere al readout dei SiPM tramite l'ASIC CITIROC-1A della WEEROC e alla gestione dei trigger di primo livello.

Le schede dovranno contenere una predisposizione e compatibilità integrale verso l'ASIC Radioroc che verrà utilizzata qualora si manifestasse disponibilità sul mercato di una versione adeguatamente testata e affidabile.

La lettura degli ASIC dovrà avvenire usando una tensione per i trigger di 1.8V e l'FPGA da utilizzare deve essere necessariamente della famiglia Artix Ultrascale+.

Ciascuna scheda avrà un routing dedicato verso i connettori per i sensori. La disposizione dei canali di readout dei SiPM Sarà fornita dal personale del GSSI al soggetto aggiudicatario della gara. Il sistema di DAQ deve rispondere alle caratteristiche riportate di seguito.

- il DAQ deve integrare un sistema per lo scrubbing del firmware in modo da poter mitigare effetti di bit-flip o similari, legati a danni da radiazione;

- l firmware dovrà essere memorizzato su una flash ridondata o distribuito da un sistema centralizzato ridondato.

- il DAQ deve essere fornito di un meccanismo di firmware upgrade ridondato tramite i due concentratori

- le operazioni di aggiornamento del firmware devono poter essere comandate a livello del ground segment con l'upload di versioni di firmware;

- il sistema deve prevedere la possibilità di ripristinare una versione di firmware funzionante;

- Le schede di DAQ dovranno poter collezionare segnali prodotti da sensori di temperatura analogici con risoluzione di almeno 0.2 °C in modo da poter effettuare una compensazione attiva della tensione di alimentazione (HV) in funzione della temperatura registrata; tale operazione viene eseguita in autonomia a livello di payload

e attuata attraverso un software ridondato. È necessario prevedere una calibrazione preliminare per l'attuazione accurata della suddetta correzione.

Dal punto di vista della lettura e integrazione del segnale, il sistema viene richiesto essere rispondente ai seguenti requisiti:

- la lettura digitale dell'ASIC CITIROC-1A dovrà avvenire in un tempo minore di 50 μs (tempo morto);

- si richiede la lettura sia del canale ad alto guadagno (HG) che del canale a basso guadagno (LG) di ciascun ASIC;

- tutte le linee di trigger dovranno essere connesse all'FPGA;

- la FPGA implementerà nel firmware un trigger topologico su tutti i canali, utilizzando la motherboard e la scheda di raccolta dati per effettuare coincidenze tra schede;

- il firmware dovrà attivare i segnali di hold dell'ASIC entro un tempo massimo di 50 ns.

Solo però a seguito di un segnale di validazione, dal concentratore si procederà alla lettura degli ASIC;

- la lettura consisterà nel memorizzare l'informazione di tutti i canali HG e LG attivi convertendoli attraverso un ADC a 14 bit, con una frequenza di campionamento di 4 MS/s per canale;

- A ciascun evento collezionato dovrà essere assegnato un timestamp, opportunamente sincronizzato al segnale PPS del sistema GPS messo a disposizione dalla piattaforma satellitare, con risoluzione di 10 ns. Il firmware dell'FPGA di DAQ trasmetterà quindi l'intero pacchetto dati al concentratore, il quale, assicurandosi del corretto timestamp, andrà a costruire l'evento. Su un canale separato, la scheda DAQ dovrà trasmettere dati di housekeeping, quali temperatura dei sensori, rate medi misurati, segnali di stato e tensioni sulla scheda. Sul canale di slow control la scheda ricevere le configurazioni degli ASIC (bitstream), configurazioni dei processi interni e pacchetto firmware per gli aggiornamenti. Tutte le comunicazioni dovranno essere protette con un sistema di controllo CRC. Il bus di comunicazione verso la motherboard dovrà prevedere delle connessioni orizzontali per distribuire il segnale di trigger tra le schede e il concentratore, due bus indipendenti per interfacciarsi con due schede di raccolta dati indipendenti (una scheda è normalmente accesa, l'altra è normalmente spenta e viene accesa solo in caso di failure della prima),

Il bus di comunicazione deve essere progettato in modo tale per cui:

- la comunicazione verso il concentratore dovrà essere LVDS;

- il bus di comunicazione prevede due canali indipendenti, uno per lo slow control e l'altro per la lettura dei dati scientifici;

- il bus di lettura dati scientifici dovrà garantire una comunicazione bidirezionale ad almeno 100 Mbps con ogni scheda. Tutte le alimentazioni richieste per l'operatività del sistema sono rese disponibili a livello di concentratore. Non sono ammissibili regolatori switching sulla scheda DAQ. Le alimentazioni devono essere postregolate tramite LDO sulla scheda DAQ

Ipotizzando schede con 128 canali (4 citiroc), saranno necessarie 640/128 = 5 schede. Si chiede di non superare questo numero di canali per schede in modo da mitigare eventuali rotture, riducendo il numero di canali perse.

#### RIDONDANZA

Nel piano B la ridondanza si ottiene come per il piano A utilizzando più schede di front-end (5) per leggere l'intero piano focale di EU-TEL. La rottura di una delle schede porta alla perdita del 20% del FOV.

Il concentratore deve essere, come nel caso A, totalmente duplicatore e tutte le schede di front-end devono provvedere a fornire due interfacce indipendenti verso i due concentratori. La rottura di uno dei concentratori deve permettere all'esperimento di procedere al 100%

## 6. Part list

Di seguito l'elenco dettagliato di tutti i componenti o parti necessari per la realizzazione della DU di ciascun modello di P/L Crystal Eye e EU-TEL. Le parti in tabella sono da intendersi a carico dell'aggiudicatario della gara. Il numero è da intendersi per ciascun modello da realizzare. L'approvvigionamento di una contingenza del 10 % è richiesto per garantire la sostituzione in caso di malfunzionamenti o fuori specifica.

## 6.1. Prototipo Crystal Eye

Il prototipo di Crystal Eye dovrà prevedere una struttura meccanica completa nella quale solo una parte sarà realmente equipaggiata (circa il 20%). La struttura meccanica completa permetterà la possibilità di testare la tecnologia di realizzazione della semisfera e di sistemare i cristalli in diverse posizioni nei test al fine di verificare gli algoritmi di trigger e event-building. Un numero sufficiente di schede DAQ, trigger board e concentratore dovranno essere forniti.

Tabella 3 Elenco materiale da acquistare per la realizzazione del prototipo di Crystal Eye a carico dell'aggiudicatario.

| ID part   | Part Number                | Descrizione                                                                                                  | Quantità                                                                                       |

|-----------|----------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| UP-p      | GAGG-F                     | Cristalli di GAGG di tipologia F<br>conformi alle dimensioni degli UP-<br>pixel del detector ottimizzato     | 20% del totale di pixel del detector ottimizzato (circa 20-30)                                 |

| DOWN-p    | LYSO                       | Cristalli di LYSO conformi alle<br>dimensioni dei DOWN-pixel del<br>detector ottimizzato                     | L 70% del fotale di nivel del detector L                                                       |

| ACS-p     | Ej-204 o BC-404            | Scintillatore plastico di forma esagonale con spessore 5mm conforme alle dimensioni del detector ottimizzato | 20% del totale di pixel del detector<br>ottimizzato (circa 20-30) + 1 lastra<br>per ACS bottom |

| SiPM-06-p | HAMAMATSU<br>S14160-6050HS | SiPM Hamamatsu Photonics, area sensibile: 6.0 mm × 6.0 mm                                                    | 2 per ogni SiPM board di lettura<br>dei cristalli. 4x(20% di<br>N_tot)+10% di spare            |

| SiPM-03-p       | HAMAMATSU<br>S14160-3050HS | SiPM Hamamatsu Photonics, area sensibile: 3.0 mm × 3.0 mm                       | 2 per ogni SiPM board di lettura<br>dei cristalli, 6 per ogni SiPM<br>board di lettura dell'ACS.<br>10x(20% di N_tot)+10% di spare |

|-----------------|----------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| SiPMboard-p     |                            | realizzazione custom in base al disegno ottimizzato                             | 3x(20% di N_tot)+ 3 spare per tipo                                                                                                 |

| DAQboard-p      |                            | realizzazione custom in base al<br>disegno ottimizzato (inclusi asic e<br>FPGA) | Transfer incomment a forming in                                                                                                    |

| Triggerboard-p  |                            | realizzazione custom in base al disegno ottimizzato                             | Numero necessario a fornire il readout completo del 20% del pixel                                                                  |

| Concentratore-p |                            | realizzazione custom in base al disegno ottimizzato                             | Numero necessario a fornire il readout completo del 20% del pixel                                                                  |

| Backplane-p     |                            | realizzazione custom in base al disegno ottimizzato                             | Numero necessario a fornire il readout completo del 20% del pixel                                                                  |

| Cavi-p          |                            | cavi segnale dalla DU alla EU e cavi comunicazione EU-pc                        | Numero necessario a fornire il readout completo del 20% del pixel                                                                  |

# 6.2. EM Crystal Eye

Di seguito la lista degli elementi necessari alla realizzazione di EM.

| ID part | Part Number                | Descrizione                                                                                              | Quantità                                                                   |

|---------|----------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| UP      | GAGG-F                     | Cristalli di GAGG di tipologia F<br>conformi alle dimensioni degli UP-<br>pixel del detector ottimizzato |                                                                            |

| DOWN    | LYSO                       | Cristalli di LYSO conformi alle<br>dimensioni dei DOWN-pixel del<br>detector ottimizzato                 | N_tot pixel del detector ottimizzato                                       |

| ACS     | Ej-204 o BC-404            | 1                                                                                                        | N_tot pixel del detector ottimizzato + lastra ACS bottom                   |

| SiPM-06 | HAMAMATSU<br>S14160-6050HS | SiPM Hamamatsu Photonics, area sensibile: 6.0 mm × 6.0 mm                                                | 2 per ogni SiPM board di lettura<br>dei cristalli. 4xN_tot+10% di<br>spare |

| SiPM-03       | HAMAMATSU<br>S14160-3050HS | SiPM Hamamatsu Photonics, area sensibile: 3.0 mm × 3.0 mm                       | 2 per ogni SiPM board di lettura<br>dei cristalli, 6 per ogni SiPM biard<br>di lettura dell'ACS.<br>10xN_tot+10% di spare |

|---------------|----------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| SiPMboard     |                            | realizzazione custom in base al disegno ottimizzato                             | 3xN_tot + 5% spare per tipo                                                                                               |

| DAQboard      |                            | realizzazione custom in base al<br>disegno ottimizzato (inclusi asic e<br>FPGA) | Numero necessario a fornire il readout completo del detector                                                              |

| Triggerboard  |                            | realizzazione custom in base al disegno ottimizzato                             | Numero necessario a fornire il readout completo del detector                                                              |

| Concentratore |                            | realizzazione custom in base al disegno ottimizzato                             | Numero necessario a fornire il readout completo del detector                                                              |

| Backplane     |                            | realizzazione custom in base al disegno ottimizzato                             | Numero necessario a fornire il readout completo del detector                                                              |

| Cavi          |                            | cavi segnale dalla DU alla EU e cavi comunicazione EU-pc                        | Numero necessario a fornire il readout completo del detector                                                              |

# **6.3. EU-TEL**

La realizzazione di EU-TEL deve tenere conto dei due possibili piani di realizzazione a seconda del tipo di ASIC utilizzato (vedi 5.6): Piano A e Piano B.

## PIANO A

| ID part              | Part Number | Descrizione                                                         | Quantità |

|----------------------|-------------|---------------------------------------------------------------------|----------|

| Scheda FPGA-FE       |             | realizzazione custom in base al progetto ottimizzato (esclusi asic) | 10       |

| Concentratore (DEMO) |             | Demoboard di debugging                                              | 3        |

| Backplane (DEMO)     |             | Demoboard di debugging                                              | 3        |

| Concentratore finale |             | realizzazione custom in base al progetto ottimizzato                | 4        |

| Backplane finale     |             | realizzazione custom in base al progetto ottimizzato                | 2        |

| EU-TEL firmware      |             | realizzazione firmware FPGA e<br>Concentratore Dati                 | 1        |

## PIANO B

| ID part Part Number | Descrizione | Quantità |

|---------------------|-------------|----------|

|---------------------|-------------|----------|

| NRE EU-TEL           | realizzazione custom in base al progetto ottimizzato                | 1  |

|----------------------|---------------------------------------------------------------------|----|

| Mezzanina EU-<br>TEL | realizzazione custom in base al progetto ottimizzato                | 12 |

| FPGA-Citiroc         | realizzazione custom in base al progetto ottimizzato (esclusi asic) | 13 |

| Concentratore        | realizzazione custom in base al progetto ottimizzato                | 5  |

| Backplane            | realizzazione custom in base al progetto ottimizzato                | 3  |

| EU-TEL firmware      | realizzazione firmware FPGA<br>Concentratore                        | 1  |

# 7. Requisiti di Progetto

In questo capitolo vengono specificati i requisiti generali di progetto, che vanno intesi come obiettivi realizzativi della fornitura. I requisiti possono essere distinti nelle seguenti categorie:

- **Requisiti di performance**: fissano le caratteristiche degli elementi attivi del P/L Zirè per garantire le capacità di rivelazione del detector desiderate;

- Requisiti ambientali: fissano le condizioni di lavoro ambientali di Crystal Eye ed EU-TEL;

- **Requisiti fisici**: fissano le caratteristiche fisiche generali di Crystal Eye ed EU-TEL, dell'interfaccia con il potenziale S/C e le caratteristiche orbitali di una potenziale missione.

# 7.1. Requisiti di Performance

| ID requisito | TITOLO                  | Descrizione                               | Commenti                                                              |

|--------------|-------------------------|-------------------------------------------|-----------------------------------------------------------------------|

| REQ-P-001A   | SiPM-ACS-TOP            | S14160-3050HS                             | SiPM Hamamatsu Photonics, area sensibile: 3.0 mm x3.0 mm              |

| REQ-P-001B   | SIPM-ACS-BOTTOM         | S14160-6050HS                             | SiPM Hamamatsu Photonics, area sensibile: 6.0 mm x 6.0 mm             |

| REQ-P-002A   | SiPM-CRYSTAL-<br>MEDIUM | S14160-3050HS                             | SiPM Hamamatsu Photonics, area sensibile: 3.0 mm x3.0 mm              |

| REQ-P-002B   | SiPM-CRYSTAL-<br>LARGE  | S14160-6050HS                             | SiPM Hamamatsu Photonics, area sensibile: 6.0 mm x 6.0 mm             |

| REQ-P-003    | ACS                     | EJ-204/BC-404                             | Scintillatore plastico Eljen EJ-204 o equivalente Saint-Gobain BC-404 |

| REQ-P-004    | UP pixel                | GAGG(Ce)-F, ESR coated, polished surfaces | Produttore: Epic Crystals                                             |

| REQ-P-005  | DOWN pixel                       | LYSO:Ce, ESR-coated, polished surfaces                                                                                                                                                          | Produttore: Epic Crystals                                                                                                                                                                                                                                                                                                                |

|------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ-P-006A | EU-ASIC                          | Citiroc 1A/Radioroc                                                                                                                                                                             | Acquisizione dati basata su ASIC CITIROC prodotto da Weeroc                                                                                                                                                                                                                                                                              |

| REQ-P-006B | EU-ASIC                          | Compatibilità con Asic<br>Radioroc                                                                                                                                                              | Le schede devono prevedere la<br>compatibilità con RADIOROC da<br>utilizzare qualora fosse disponibile<br>nei tempi opportuni sul mercato                                                                                                                                                                                                |

| REQ-P-007  | EU-DAQ                           | Uso di Zynq Ultrascale+                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                          |

| REQ-P-008  | EU-Concentratore                 | La scheda deve essere<br>progettata per leggere almeno<br>10 DAQ board                                                                                                                          |                                                                                                                                                                                                                                                                                                                                          |